Capacitive Controller ICs Capacitive Switch Controller ICs

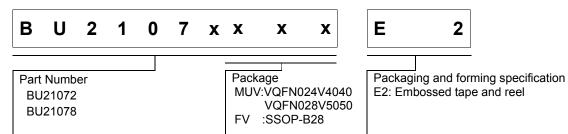

BU21072MUV / BU21078MUV / BU21078FV

## **General Description**

BU21072MUV/BU21078MUV/BU21078FV is a capacitive sensor controller for switch operation. In addition to a regular simple switch, support matrix switches which are arranged in the matrix sensors. If external noise and temperature drift are detected, the automatic self-calibration is operated. Include LED controller with PWM function.

#### Features

- 10 capacitive sensor ports. (BU21072MUV)

12 capacitive sensor ports. (BU21078MUV / BU21078FV)

- Supported Matrix switches. Maximum 16 switches. (BU21072MUV)

Maximum 36 switches. (BU21078MUV / BU21078FV)

- Automatic self-calibration.

- Continued touch detection.

- LED controller with PWM function.

- Inform the detected result of switch operation by interrupt.

- 2-wire serial bus interface.

- Single power supply.

- Built-in Power-On-Reset and Oscillator.

#### Applications

- Appliance that require multiple switches.

- Information appliance as printer.

- AV appliance as digital TV and HDD recorder.

- Notebook PC.

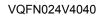

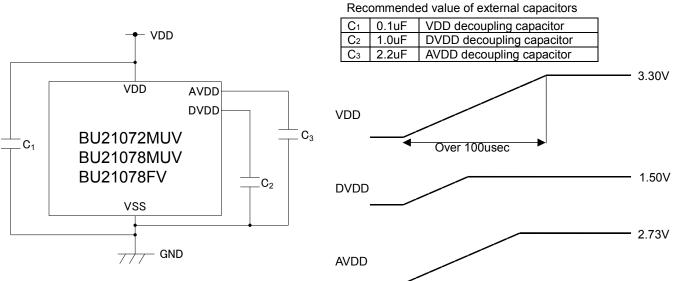

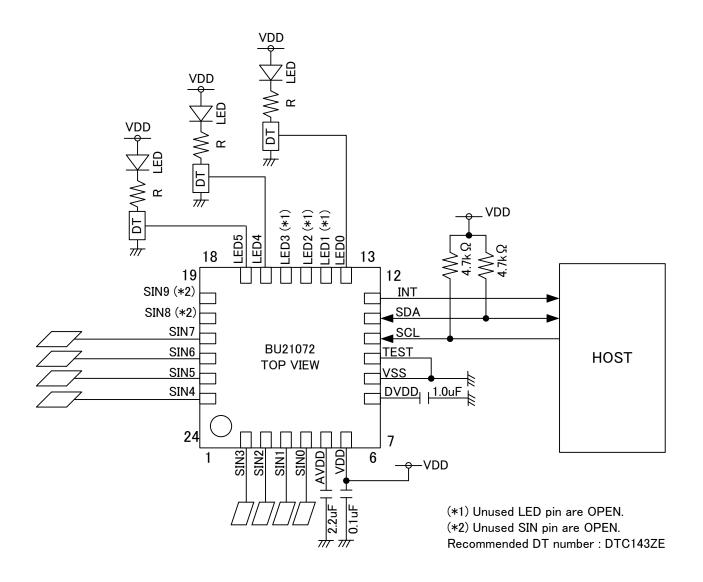

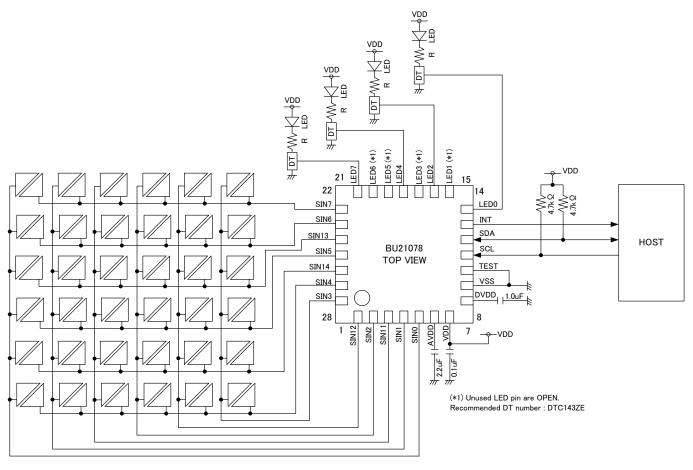

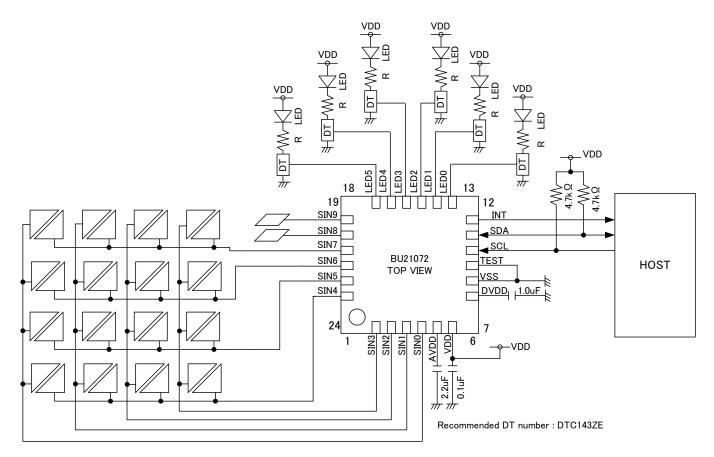

#### **Typical Application Circuit**

#### Key Specifications

- Input voltage range

Operating temperature range

3.0 to 5.5V

Operating temperature range

-20 to 85°C

- Operating current 3.5mA (Typ.)

- O a a marta

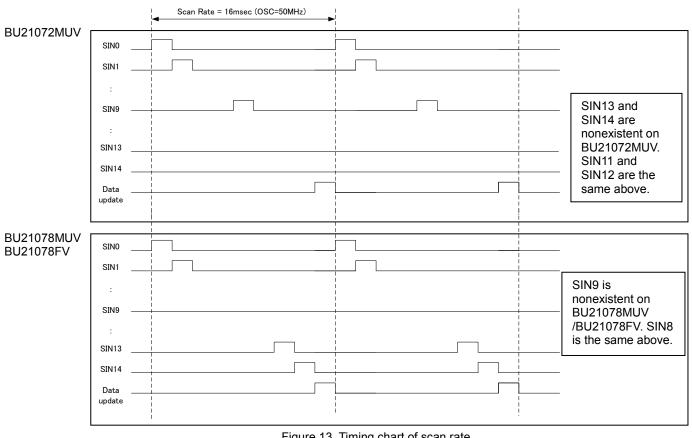

- Scan rate

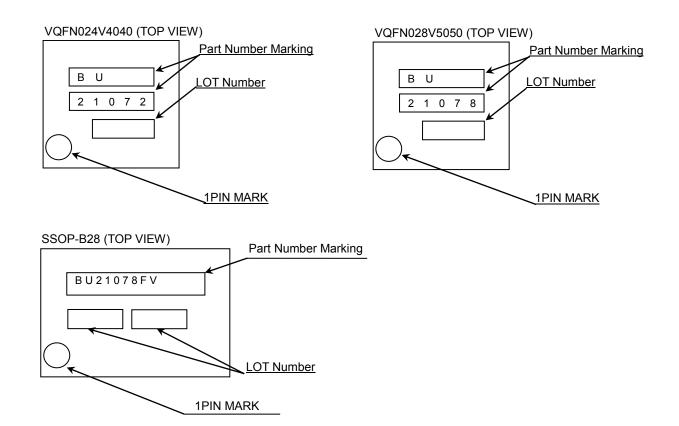

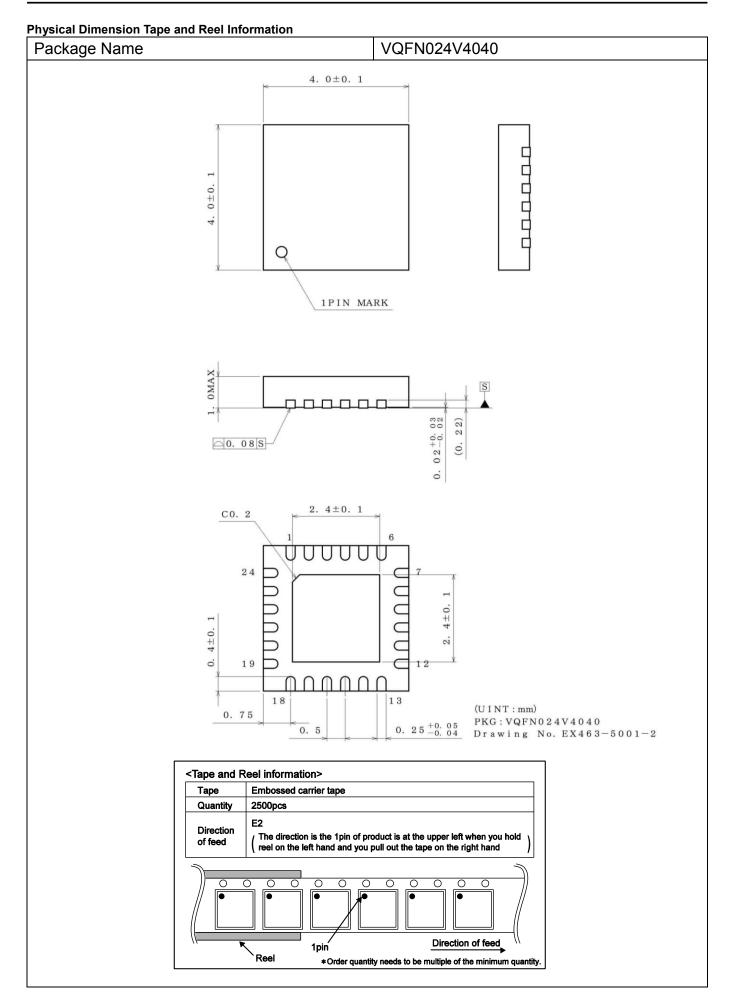

#### Packages

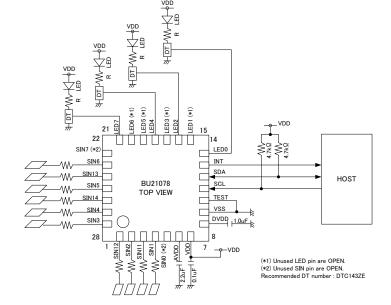

- BU21072MUV : VQFN024V4040

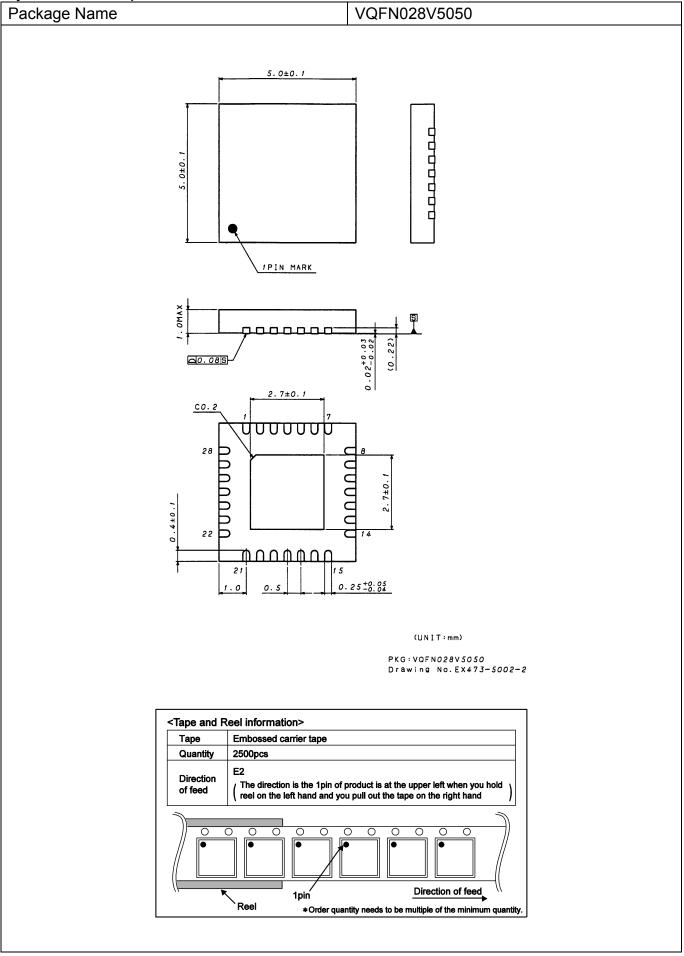

- BU21078MUV : VQFN028V5050

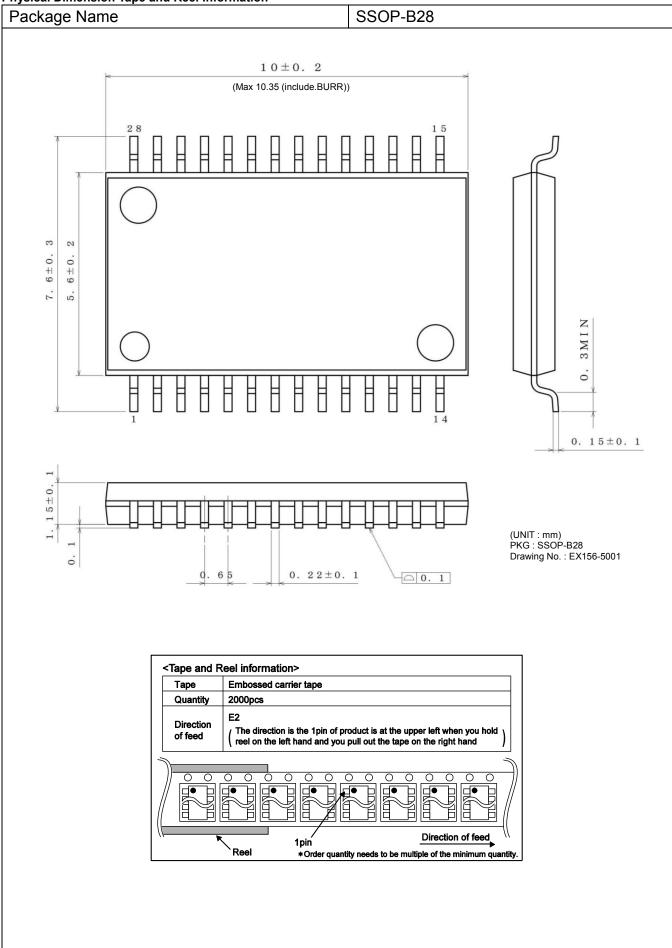

- BU21078FV : SSOP-B28

4.00 mm×4.00 mm×1.00 mm

5.00 mm×5.00 mm×1.00 mm

10.00 mm×7.60 mm×1.35 mm

16msec (Typ.)

VQFN028V5050

SSOP-B28

Figure 1. Typical Application Circuit

● Product structure : Silicon monolithic integrated circuit ● This product is not designed protection against radioactive rays

#### OVERVIEW

BU21072MUV/BU21078MUV/BU21078FV is a capacitive sensor controller for switch operation.

Included blocks are AFE (Analog Front End) detecting capacitance, A/D converter, MPU, LED ports with PWM function, 2-wire serial bus interface compatible with I2C protocol, power-on-reset, oscillator. Operate with a 3.0 to 5.5V single power supply.

The results that detected switch operations (Touch/Release/Hold) are held to each register. An interrupt is send from INT port to the host when a register is updated by detected operations. If external noise and temperature drift are detected, run automatic self-calibration. Without periodic polling, offer the reduction of the host load.

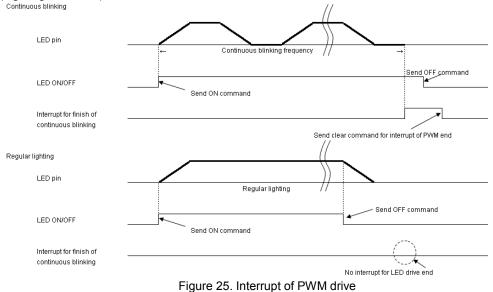

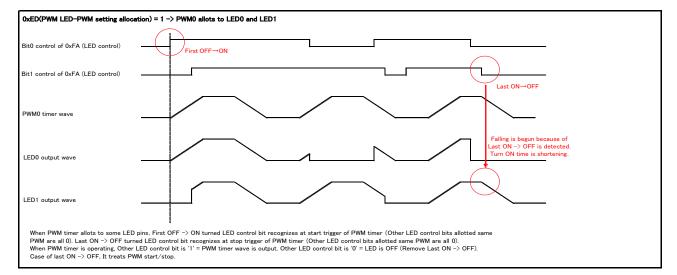

LED ports are able to be applied PWM function. PWM function offers fade-in / fade-out brightness control.

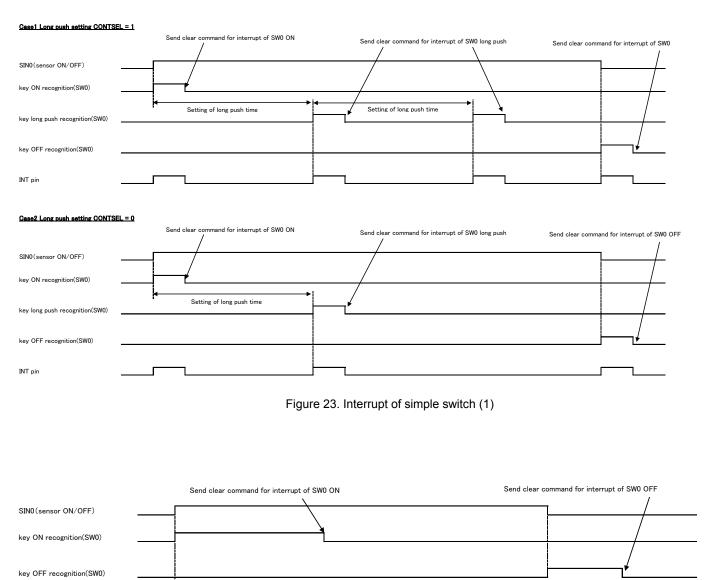

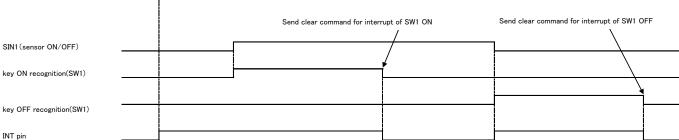

#### Simple switch

One sensor is assigned to one switch. Each simple switch has the registers of detected Touch/Release/Hold operations. Simple switches support to multi-detect Touch/Release/Hold. Unused simple switches are maskable.

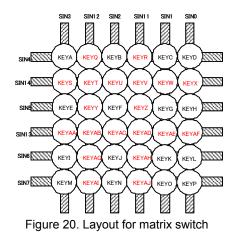

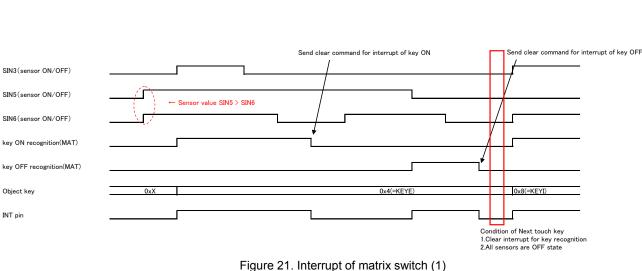

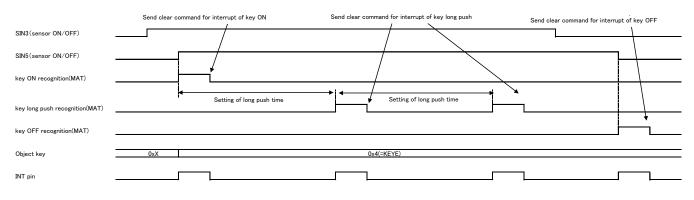

#### Matrix switches

The cross points of the sensors which are arranged in a matrix are able to assigned to individual switches. Each matrix switch has the registers of detected Touch/Release/Hold operations. Matrix switches do not support to multi-detect Touch/Release/Hold. Not used matrix switches are maskable. BU21072MUV supports 16 matrix switches configured by 4x4 sensors, and BU21078MUV / BU21078FV supports 36 matrix switches configured by 6x6 sensors.

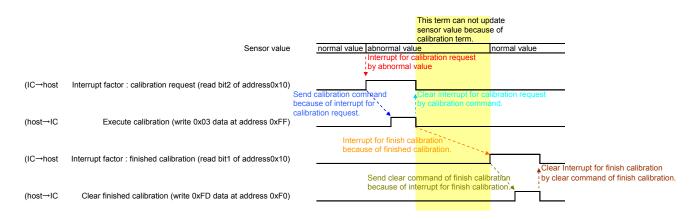

#### Automatic self-calibration

BU21072MUV/BU21078MUV/BU21078FV has observed the situation surrounding the sensor based on the detection result. If external noise and temperature drift are detected, the automatic self-calibration is operated for the stable detection result.

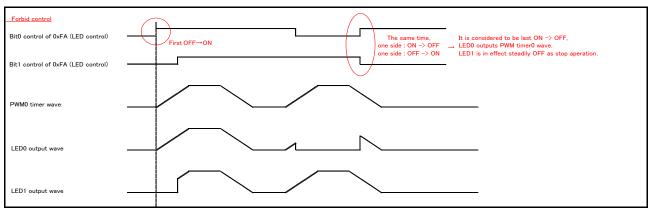

#### LED controller with PWM timers

LED controller is High active. Each LED port is assigned to a choice of four PWM timers. If the situation surrounding the sensor is changed by the switching LED, it is useable that calibration is operated by sending LED control command.

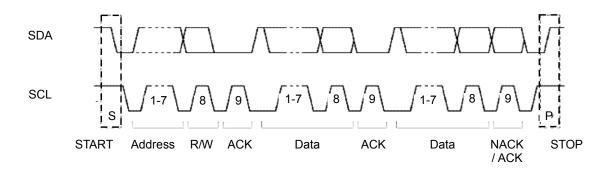

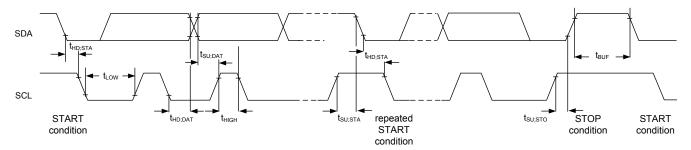

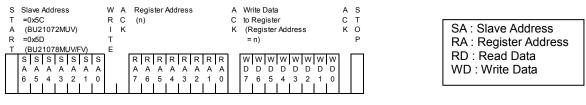

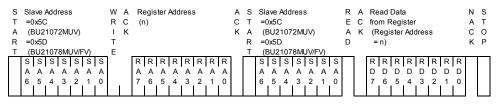

Host interface

BU21072MUV/BU21078MUV/BU21078FV is slave device for the host device. 2-wire serial bus is compatible with I2C protocol.

Slave Address : 0x5C(BU21072MUV) , 0x5D(BU21078MUV / BU21078FV)

#### **Pin Configurations**

## **Pin Descriptions**

|            | Number     |           | Nama  | Turne | Function                      | Nete                          | Devices | Initial   | I/O                     |

|------------|------------|-----------|-------|-------|-------------------------------|-------------------------------|---------|-----------|-------------------------|

| BU21072MUV | BU21078MUV | BU21078FV | Name  | Туре  | Function                      | Note                          | Power   | Condition | Equivalence<br>Circuits |

| -          | 1          | 11        | SIN12 | Ain   | Capacitive Touch Sensor12     |                               | AVDD    | Hi-Z      | Fig.5                   |

| 2          | 2          | 12        | SIN2  | Ain   | Capacitive Touch Sensor2      |                               | AVDD    | Hi-Z      | Fig.5                   |

| -          | 3          | 13        | SIN11 | Ain   | Capacitive Touch Sensor11     |                               | AVDD    | Hi-Z      | Fig.5                   |

| 3          | 4          | 14        | SIN1  | Ain   | Capacitive Touch Sensor1      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 4          | 5          | 15        | SIN0  | Ain   | Capacitive Touch Sensor0      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 5          | 6          | 16        | AVDD  | Power | LDO output for analog blocks  |                               | VDD     | -         | -                       |

| 6          | 7          | 17        | VDD   | Power | Power                         |                               | -       | -         | -                       |

| 7          | 8          | 18        | DVDD  | Power | LDO output for digital blocks |                               | VDD     | -         | -                       |

| 8          | 9          | 19        | VSS   | GND   | Ground                        |                               | -       | -         | -                       |

| 9          | 10         | 20        | TEST  | In    | Test input                    | Please connect to Ground leve | VDD     | -         | Fig.6                   |

| 10         | 11         | 21        | SCL   | InOut | Host I/F clock input          |                               | VDD     | Hi-Z      | Fig.6                   |

| 11         | 12         | 22        | SDA   | InOut | Bi-directional Host I/F Data  |                               | VDD     | Hi-Z      | Fig.6                   |

| 12         | 13         | 23        | INT   | Out   | Interrupt output              | Active High Interrupt         | VDD     | "L"       | Fig.7                   |

| 13         | 14         | 24        | LED0  | Out   | LED control with PWM output0  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| 14         | 15         | 25        | LED1  | Out   | LED control with PWM output1  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| 15         | 16         | 26        | LED2  | Out   | LED control with PWM output2  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| 16         | 17         | 27        | LED3  | Out   | LED control with PWM output3  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| 17         | 18         | 28        | LED4  | Out   | LED control with PWM output4  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| 18         | 19         | 1         | LED5  | Out   | LED control with PWM output5  | Active High                   | VDD     | Hi-Z      | Fig.7                   |

| -          | 20         | 2         | LED6  | Out   | LED control with PWM output6  | Active High                   | VDD     | "L"       | Fig.7                   |

| -          | 21         | 3         | LED7  | Out   | LED control with PWM output7  | Active High                   | VDD     | "L"       | Fig.7                   |

| 19         | -          | -         | SIN9  | Ain   | Capacitive Touch Sensor9      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 20         | -          | -         | SIN8  | Ain   | Capacitive Touch Sensor8      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 21         | 22         | 4         | SIN7  | Ain   | Capacitive Touch Sensor7      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 22         | 23         | 5         | SIN6  | Ain   | Capacitive Touch Sensor6      |                               | AVDD    | Hi-Z      | Fig.5                   |

| -          | 24         | 6         | SIN13 | Ain   | Capacitive Touch Sensor13     |                               | AVDD    | Hi-Z      | Fig.5                   |

| 23         | 25         | 7         | SIN5  | Ain   | Capacitive Touch Sensor5      |                               | AVDD    | Hi-Z      | Fig.5                   |

| -          | 26         | 8         | SIN14 | Ain   | Capacitive Touch Sensor14     |                               | AVDD    | Hi-Z      | Fig.5                   |

| 24         | 27         | 9         | SIN4  | Ain   | Capacitive Touch Sensor4      |                               | AVDD    | Hi-Z      | Fig.5                   |

| 1          | 28         | 10        | SIN3  | Ain   | Capacitive Touch Sensor3      |                               | AVDD    | Hi-Z      | Fig.5                   |

Initial Condition is at that power-on-reset is active.

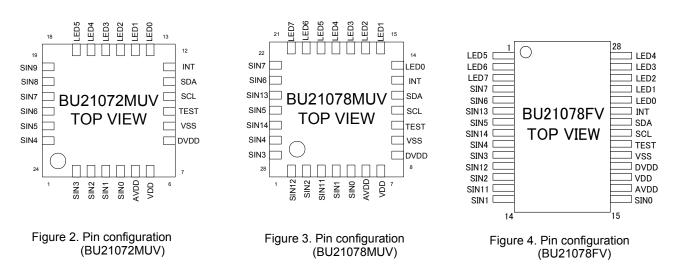

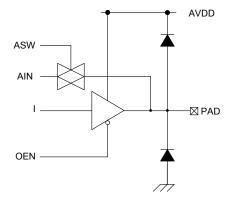

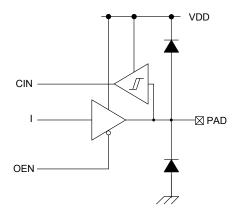

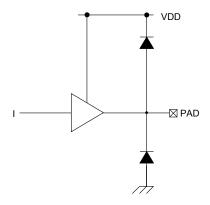

## I/O Equivalence Circuits

Figure 5. I/O equivalence circuit (a)

Figure 6. I/O equivalence circuit (b)

Figure 7. I/O equivalence circuit (c)

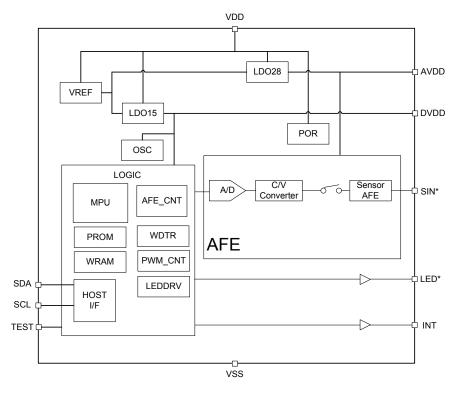

## **Block Diagram**

Figure 8. Block Diagram

## **Description of Blocks**

Sensor AFE, C/V Converter

Convert from capacitance to voltage following the order of sensors.

A/D

Convert from voltage to the detected result the digital value.

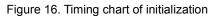

LDO28

2.73V output LDO for Sensor AFE, C/V Converter and A/D.

LDO15

1.5V output LDO for OSC and digital blocks.

OSC Ring oscillator as the system clock.

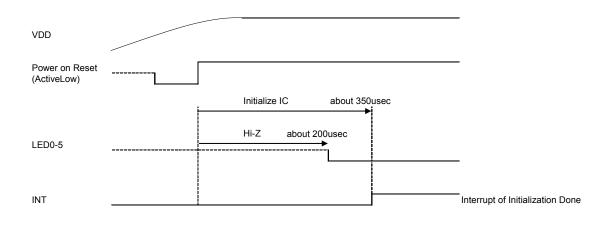

POR

Power-On-Reset monitoring VDD as the system reset.

MPU

Based on the detection result, detect switch operations (Touch/Release/Hold) and run Auto-calibration. Inform by the INT port to the host about that the switch operations are detected. LED ports are controlled by the commands from the host.

PROM

Program ROM for the included MPU.

WRAM

Work RAM for the included MPU.

HOST I/F 2-wire serial bus interface compatible with I2C protocol.

AFE CNT

Sequencer of Sensor AFE, C/V converter and A/D.

PWM\_CNT

PWM timers for the LED ports.

LEDDRV

LED port drivers.

WDTR

Watchdog Timer Reset. It releases the system reset after 1 sec from that MPU cannot clear WDTR. (If MPU cannot clear WDTR, MPU is hang-up.)

## Absolute Maximum Ratings (Ta = 25°C)

| Param                     | eter       | Symbol            | Rating            | Unit |

|---------------------------|------------|-------------------|-------------------|------|

| Power supply voltage      | 9          | VDD               | -0.5 to 7.0       | V    |

| Input voltage             |            | V <sub>IN</sub>   | -0.5 to VDD + 0.3 | V    |

| Storage temperature range |            | T <sub>stg</sub>  | -55 to 125        | °C   |

|                           | BU21072MUV |                   | 272 *1            |      |

| Power dissipation         | BU21078MUV | Pd                | 304 <sup>*2</sup> | mW   |

| BU21078FV                 |            |                   | 640 <sup>*3</sup> |      |

| Maximum junction te       | mperature  | T <sub>jmax</sub> | 125               | °C   |

Derated by 2.72mW/°C over 25°C. (IC only). Derated by 3.04mW/°C over 25°C. (IC only). Derated by 6.4mW/°C over 25°C. (IC only). \*1

\*2 \*3

## **Recommended Operating Ratings**

| Parameter                   | Symbol           | Rating     | Unit |

|-----------------------------|------------------|------------|------|

| Power supply voltage        | VDD              | 3.0 to 5.5 | V    |

| Operating temperature range | T <sub>opr</sub> | -20 to 85  | °C   |

## Electrical Characteristics (Ta = 25°C , VDD = 3.3V , VSS = 0V)

| Parameter                      | Symbol            |           | Rating |           | Unit | Condition                |

|--------------------------------|-------------------|-----------|--------|-----------|------|--------------------------|

| Faranielei                     | Symbol            | Min.      | Тур.   | Max.      | Onit | Condition                |

| Input High voltage             | VIH               | VDD x 0.7 | -      | VDD + 0.3 | V    |                          |

| Input Low voltage              | VIL               | VSS - 0.3 | -      | VDD x 0.3 | V    |                          |

| Output High voltage            | V <sub>OH</sub>   | VDD - 0.5 | -      | VDD       | V    | I <sub>OH</sub> = -4mA   |

| Output Low voltage             | V <sub>OL</sub>   | VSS       | -      | VSS + 0.5 | V    | I <sub>OL</sub> = 4mA    |

| Oscillator clock frequency     | f <sub>OSC</sub>  | 45        | 50     | 55        | MHz  |                          |

| DVDD LDO output voltage        | V <sub>DVDD</sub> | 1.35      | 1.50   | 1.65      | V    |                          |

| AVDD LDO output voltage        | V <sub>AVDD</sub> | 2.63      | 2.73   | 2.83      | V    |                          |

| Power-on-reset release voltage |                   | 2.25      | -      | 2.55      | V    |                          |

| Power-on-reset detect voltage  |                   | 2.10      | -      | 2.40      | V    |                          |

| Operating current              | I <sub>DD</sub>   | -         | 3.5    | -         | mA   | Without load of sensors. |

## Register Map (OSC = 50MHz , unless otherwise noted) No accessing to the reserved areas is allowed.

| Group             | Address           | Name                    | R/W    | Ini          | 7            | 6                         | 5           | 4                         | 3           | 2           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0        |

|-------------------|-------------------|-------------------------|--------|--------------|--------------|---------------------------|-------------|---------------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                   | 0×00              | SIN_DATA                | R      | 0×00         | SD_SIN0[7]   | SD_SIN0[6]                | SD_SIN0[5]  | SD_SIN0[4]                | SD_SIN0[3]  | SD_SINO[2]  | SD_SIN0[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN0  |

|                   | 0×01              | SIN_DATA                | R      | 0×00         | SD_SIN1[7]   | SD_SIN1[6]                | SD_SIN1[5]  | SD_SIN1[4]                | SD_SIN1[3]  | SD_SIN1[2]  | SD_SIN1[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN1  |

|                   | 0×02              | SIN_DATA                | R      | 0x00         | SD_SIN2[7]   | SD_SIN2[6]                | SD_SIN2[5]  | SD_SIN2[4]                | SD_SIN2[3]  | SD_SIN2[2]  | SD_SIN2[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN2[ |

|                   | 0×03              | SIN_DATA                | R      | 0×00         | SD_SIN3[7]   | SD_SIN3[6]                | SD_SIN3[5]  | SD_SIN3[4]                | SD_SIN3[3]  | SD_SIN3[2]  | SD_SIN3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN3  |

|                   | 0×04              | SIN_DATA                | R      | 0×00         | SD_SIN4[7]   | SD SIN4[6]                | SD_SIN4[5]  | SD SIN4[4]                | SD SIN4[3]  | SD_SIN4[2]  | SD_SIN4[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD SIN4  |

|                   | 0×05              | SIN_DATA                | R      | 0×00         | SD_SIN5[7]   | SD_SIN5[6]                | SD_SIN5[5]  | SD_SIN5[4]                | SD_SIN5[3]  | SD_SIN5[2]  | SD SIN5[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN5  |

|                   | 0×06              | SIN_DATA                | R      | 0×00         | SD_SIN6[7]   | SD SIN6[6]                | SD_SIN6[5]  | SD_SIN6[4]                | SD_SIN6[3]  | SD_SIN6[2]  | SD_SIN6[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN6  |

|                   | 0×07              | SIN_DATA                | R      | 0×00         | SD_SIN7[7]   | SD_SIN7[6]                | SD_SIN7[5]  | SD_SIN7[4]                | SD_SIN7[3]  | SD_SIN7[2]  | SD_SIN7[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN7  |

| Detect value      | 0×08              | SIN_DATA                | R      | 0×00         | SD_SIN8[7]   | SD_SIN8[6]                | SD_SIN8[5]  | SD_SIN8[4]                | SD_SIN8[3]  | SD_SIN8[2]  | SD_SIN8[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN8  |

|                   | 0×00              | SIN_DATA                | R      | 0×00         | SD_SIN9[7]   | SD_SIN9[6]                | SD_SIN9[5]  | SD_SIN9[4]                | SD_SIN9[3]  | SD_SIN9[2]  | SD_SIN9[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIN9  |

|                   | 0x03              | SIN_DATA                | R      | 0×00         | SD_SIND[7]   | SD_SINJ[0]<br>SD_SINJ0[6] | SD_SIN10[5] | SD_SINJ[4]<br>SD_SIN10[4] | SD_SIN10[3] | SD_SIN0[2]  | SD_SIN0[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SD_SIND  |

|                   |                   | _                       |        |              | _            |                           |             |                           |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|                   | 0×0B              | SIN_DATA                | R      | 0x00         | SD_SIN11[7]  | SD_SIN11[6]               | SD_SIN11[5] | SD_SIN11[4]               | SD_SIN11[3] | SD_SIN11[2] | SD_SIN11[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD_SIN1  |

|                   | 0x0C              | SIN_DATA                | R      | 0×00         | SD_SIN12[7]  | SD_SIN12[6]               | SD_SIN12[5] | SD_SIN12[4]               | SD_SIN12[3] | SD_SIN12[2] | SD_SIN12[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD_SIN12 |

|                   | 0×0D              | SIN_DATA                | R      | 0×00         | SD_SIN13[7]  | SD_SIN13[6]               | SD_SIN13[5] | SD_SIN13[4]               | SD_SIN13[3] | SD_SIN13[2] | SD_SIN13[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD_SIN13 |

|                   | 0×0E              | SIN_DATA                | R      | 0×00         | SD_SIN14[7]  | SD_SIN14[6]               | SD_SIN14[5] | SD_SIN14[4]               | SD_SIN14[3] | SD_SIN14[2] | SD_SIN14[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD_SIN14 |

|                   | 0×0F              | SIN_DATA                | R      | 0×00         | SD_SIN15[7]  | SD_SIN15[6]               | SD_SIN15[5] | SD_SIN15[4]               | SD_SIN15[3] | SD_SIN15[2] | SD_SIN15[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD_SIN1  |

|                   | 0×10              | INTERRUPT               | R      | 0×00         | CONTDET      | OFFDET                    | ONDET       | PERCAL                    | PWM         | ERCAL       | CAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INI      |

|                   | 0×11              | STATE_SIN               | R      | 0×00         | SIN7         | SIN6                      | SIN5        | SIN4                      | SIN3        | SIN2        | SIN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SINO     |

|                   | 0×12              | STATE_SIN               | R      | 0×00         | SIN15        | SIN14                     | SIN13       | SIN12                     | SIN11       | SIN10       | SIN9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SINS     |

|                   | 0×13              | DETECT_ON               | R      | 0×00         | S₩7          | SW6                       | SW5         | S₩4                       | S#3         | SW2         | SW1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S#0      |

|                   | 0×14              | DETECT_ON               | R      | 0×00         | SW15         | SW14                      | SW13        | SW12                      | SW11        | SW10        | SW9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S#8      |

|                   | 0×15              | DETECT_ON               | R      | 0×00         | MAT          | -                         | KEY[5]      | KEY[4]                    | KEY[3]      | KEY[2]      | KEY[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | KEY [C   |

|                   | 0×16              | DETECT_OFF              | R      | 0×00         | S₩7          | SW6                       | SW5         | S#4                       | SW3         | SW2         | SW1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SWO      |

| tect result       | 0×17              | DETECT_OFF              | R      | 0×00         | SW15         | SW14                      | SW13        | SW12                      | SW11        | SW10        | SW9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S#8      |

|                   | 0×18              | DETECT_OFF              | R      | 0×00         | MAT          | -                         | KEY[5]      | KEY[4]                    | KEY[3]      | KEY[2]      | KEY[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | KEY [0   |